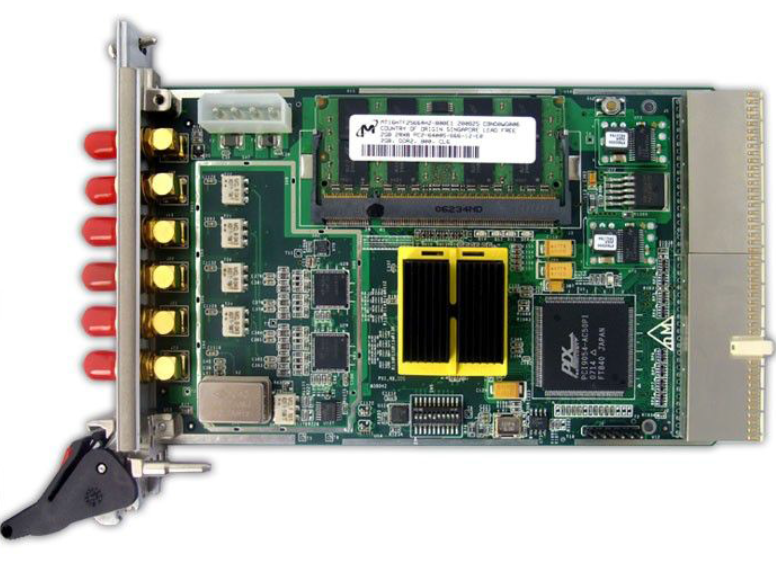

1、板卡概述

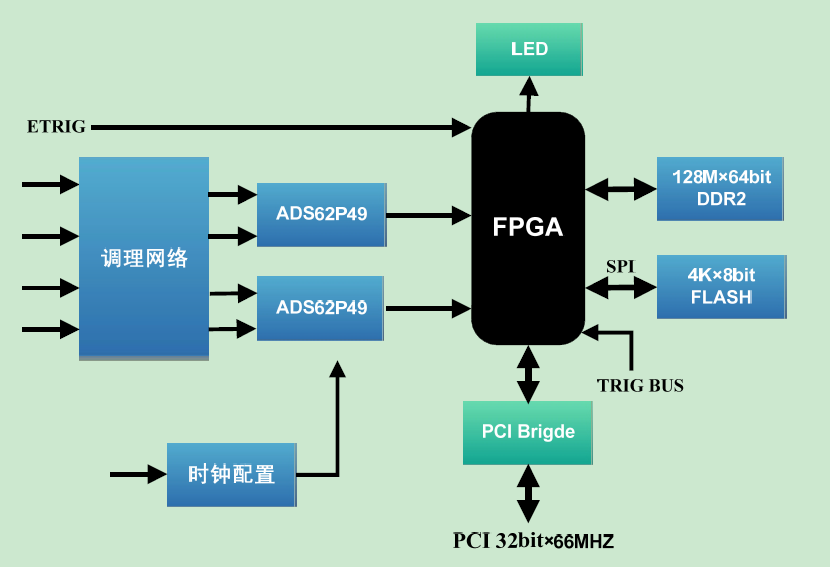

本板卡是基于PXI 高速AD 采集卡的总体设计方案。用FPGA 完成的数据采集和控制、存储管理和

PCI 的接口转换。主要接口分为模拟接口部分、AD 转换部分、DDR2 接口部分、PCI 接口部分,同步触

发接口和SPI FLASH。

2、功能和技术指针

1.大小:3U PXI 板;

2.通道数目:4 通道差分输入同步采集。1 路数字外触发信道。

3.采样率:最大250Mbps;

4.输入类型:差分输入,0~±1V,变压器滤波输入

5.AD 位数:14 位。

6.板载内存:2G Byte;

7.E2PROM 资料存储:可将一小部分数据存在板上,4KB 大小

8.读数误差:0.1%。(标定后)

9.量程:0~±1V

10.触发方式:1,通道双电平触发。2,外触发。3 软件触发

11.同步:提供多板同步。

12.采集方式:

a) 连续(高速时写满内存为止或循环缓冲)

b) 瞬态(无触发信号时循环缓冲,有触发信号时采集,可设置采集长度及触发位置)

c) 双速率(无触发信号时低速采集(直接传至PC 存储)有触发信号时高速采集,可设置采集长度及

触发位置)

13.DMA 方式:Scatter-gather DMA

14.AD 芯片同类型功能,同封装兼容:

ADS62P49(250M 14bit), ADS62P29(250M 12bit),

ADS62P48(200M 14bit), ADS62P28(200M 12bit)

SPI 位置修改兼容以下设计

ADS62P45(125M 14bit), ADS62P25(125M 12bit),

ADS62P44(105M 14bit), ADS62P24(105M 12bit),

ADS62P43(80M 14bit), ADS62P23(80M 12bit),ADS62P42(65M 14bit), ADS62P22(65M 12bit)

3、硬件系统组成

系统的核心部分在于用FPGA 完成的数据采集和控制、存储管理和PCI 的接口转换。主要接口分

为模拟接口部分、AD 转换部分、DDR2 接口部分、PCI 接口部分,同步触发接口和SPI

FLASH。

(1) 主FPGA

FPGA 是整个系统的核心部分,选择型号为xilinx 公司V5 系列XC5VLX30-1FFG676。支持

DDR2-400 内存条SODIMM 接口。在FPGA 内实现抽取滤波算法,有丰富的乘法器资源。

(2) ADC

选择TI 公司的ADS62P49 芯片,该芯片为14bit 高速ADC,可以支持到最高250M 采样率,并且同

时支持DDR LVDS 接口,与FPGA 能够进行良好的连接。

(3) DDR2 内存条

选择MICRON 公司DDR2 模块:型号MT16HTF25664HZ-667。该内存条接口和笔记本内存条兼容。

(4) PCI bridge

PCI 桥作为PXI 的PCI 接口与FPGA 进行数据交换的信道,32bit,33M/66M 相容。采用PLX 桥芯

片PCI9056。

4、软件支持

(1) FPGA 程序支持DDR2 读写,AD 采集,同步控制,触发采集。

(2) 客户端支持window XP ,Linux 开发,客户端应用测试程序。

6、物理特性:

工作温度:商业级0℃~ +55℃ ,工业级-40℃~ +85℃

工作湿度:10%~80%→

7、供电要求:

双直流电源供电。电压: +3.3V 5V。总功耗15W。

8、应用领域

雷达、软件无线电、图像数据采集。