一、板卡概述:

本技术开发主要是支持客户完成基于 TI DSP TMS320C6678 芯片和 Xilinx 公司 Kintex 7 系列芯片设 计基于 6U CPCIe 结构的高速通用接口板卡。

二、功能和技术指标:

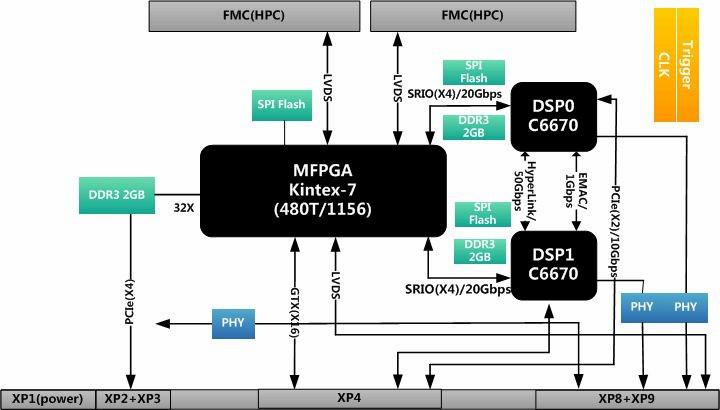

•板卡为 6U CPCIe 结构,板卡底板接插件采用 CPCIe 类型的高速串行接插件。

•DSP0 和 DSP1 各挂载 2Gbyte 的 DDR3-SDRAM;DSP0 和 DSP1 各挂载 1 片 SPI Flash 用于存储自身配 置文件; DSP0 和 DSP1 之间使用 Hyperlink 和 EMAC 互连;DSP0、DSP1 各实现 1 个千兆以太网接口, 从后背板 XP9 对外连接,用于系统级调试和通信控制;DSP0、DSP1 通过 PCIe(X2)连接至后背板 XP4, 用于板间互联;

•FPGA 用于并行高速计算和高速互联,以及两片 DSP 的程序加载方式控制和监控等功能;MFPGA 挂 载一组容量为 2Gbyte、接口数据位宽为 32bits 的 DDR3-SDRAM;MFPGA 可通过 SPI Flash 加载自身 配置文件; MFPGA 与 DSP0、DSP1 间使用 RapidIO 互连,共占用 MFPGA 8 个 GTX;MFPGA 中的 16 个 GTX 与背板连接器 XP4 互联;; MFPGA 通过 LVDS 自定义信号外接两个 FMC(HPC)接口;MFPGA 与后 背板(XP8+XP9)通过 LVDS 自定义总线互联;

•MFPGA 实现 1 个 4x 的 PCIe 接口用于与系统主板互联,可实时接收 MFPGA 的配置文件;

•板卡具有复位按钮和指示灯;

•板卡 Trigger 和 CLK 信号从前面板的 SMA 接口输入;

•板卡设计芯片目前使用商业级,要求兼容工业级设计。

三、软件内容:

1. 提供 MFPGA 与两片 DSP 通信的 RapidIO 测试程序。

2. 提供 CFPGA 与上位机通信的 PCIe 测试程序。

3. 提供 DDR3 接口测试程序

1) 支持 PCIe 驱动。

2) DSP 支持千兆网络传输,移植 LWIP 协议栈,支持 ping,TCP、UDP、IP 传输协议。

3) DSP 支持 Flash 引导方式。

2、(8)基于 CPCI Express 的双 TMS320C6678 + XC7K420T 的高速数据处理平台

一、板卡概述

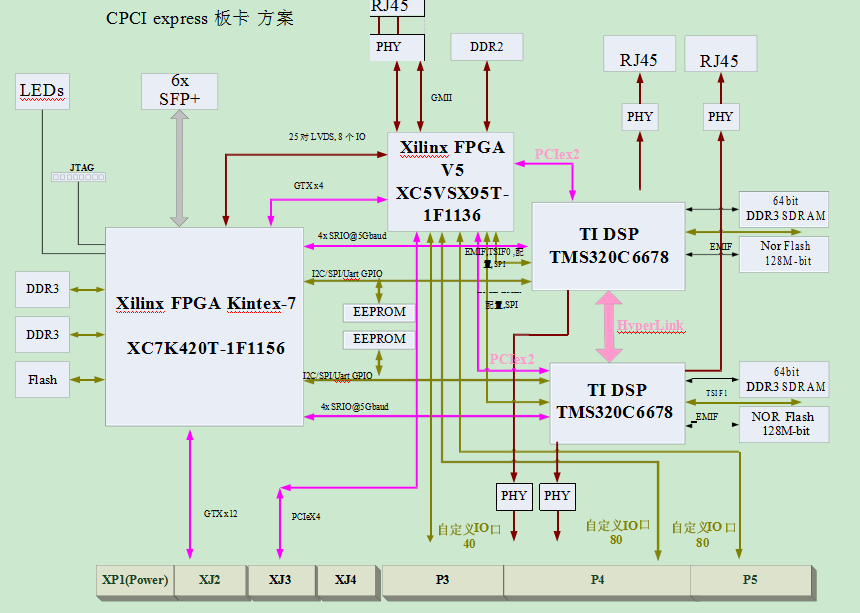

板卡由我公司自主研发,基于 6U CPCIe 架构,处理板包含两片 TI DSP TMS320C6678 芯片;一片 Xilinx 公司 FPGA XC7K420T-1FFG1156 芯片;六个千兆光纤接口;DSP 与 FPGA 之间 RapidIOX4 互联, DSP 之间 Hyperlink X4 互联;FPGA 提供 12 个 GTX 连于背板(GTX 支持 6.25Gbps 的传输频率);每 颗 DSP 外接 1GB 的 DDR3,64bit 位宽,32MB Nor Flash;FPGA 外接 2 组 DDR3,各 512MB,64bit 位 宽,32MB Nor Flash;通过 PCIe 桥连接 DSP 的 PCIe 和 FPGA 的 PCIe 口,PCIe 对外 X4 模式;FPGA 连接不少于 160 根普通 IO 到 CPCIe 的 P4,P5 连接器。

二、处理板技术指标

(1) 板卡采用两片 TI DSP TMS320C6678 芯片,8 核,主频 1G。

(2) 板卡采用 Xilinx 公司 FPGA XC7K420T-1FFG1156 芯片。

(3) 前面板 两个 DSP 各出一个千兆网口,另外 2 个网络连于背板。

(4) 前面板 FPGA 出两个千兆网口,6 个 SFF 模块光纤,支持 5Gbps

(5) 前面板出 4 个指示灯,1 个复位按钮。

(6) DSP 与 FPGA 之间 RapidIOX4 互联,DSP 的 Uart,SPI,I2C 连接于 FPGA。

(7) DSP 之间 Hyperlink X4 互联。

(8) FPGA 提供 12 个 GTX 连于背板,支持 4 个 X2,1 个 X4 的工作模式配置。GTX 最高工作频率为

6.25Gbps。

(9) 每颗 DSP 外接 1GB 的 DDR3,64bit 位宽;32MB Nor Flash.

(10) FPGA 外接 2 组 DDR3,各 512MB,64bit 位宽,32MB Nor Flash,在原理图设计阶段,如 FPGA 的

I/O 引脚资源不够,则可将 DDR3 位宽调整为 32BIT 宽。

(11) DSP 支持远程网络加载,PCIe 加载;FPGA 支持 Master SelectMAP 和 Master BPI 加载,同时支持 DSP0

或者 DSP1 的 SPI 口对 FPGA 进行动态加载和对配置芯片程序更新。

(12) FPGA 连接不少于 160 根普通 IO 到 CPCIe 的 P4,P5 连接器。

(13) FPGA 能读取背板槽位信息,ID[3:0]。

(14) FPGA 外接 E2PROM。

(15) 板卡芯片要求工业级。

(16) 供电 采用 +5V +12V 双电源。 (17) 板卡结构标准 CPCIe 6U 大小。 (18) 整板冷却,支持加固。

三、软件系统

DSP 底层软件包括:

(1)DSP 的 DDR3 测试程序;

(2)DSP 的 Nor Flash 擦写程序;

(3)DSP 的网络接口测试,SGMII 互传程序;

(4)DSP 的 HyperLink 互连传输程序;

(5)DSP 的 SPI 接口程序;

(6)DSP 的 I2C E2PROM 操作程序;

(7)DSP 的 RapidIO 接口驱动程序;

(8)DSP 的多核加载测试程序;

(9)DSP 的网络加载程序;

(10)DSP 的 GPIO 中断服务测试程序;

(11) DSP 对 FPGA 的动态加载和配置程序更新程序;

FPGA 底层软件包括:

(1)FPGA 的 DDR3 驱动接口程序;

(2)FPGA 的网络接口驱动程序;

(3)FPGA 的 Nor Flash 接口驱动程序;

(4)FPGA 与 DSP 的 RapidIO 驱动程序;

(5)与背板互连 DSP 板卡的 GTX 传输程序;

(6)FPGA 的光纤接口驱动程序;

(7)从 FPGA 的电源管理,时钟管理,复位管理等配置管理程序。

四、物理特性:

尺寸:6U CPCIe 板卡,大小为 160 x 233.35mm。 工作 温度:0℃~ +55℃ ,支持工业级 -40℃~ +85℃ 工 作湿度:10%~80%

五、供电要求: 双直流电源供电。整板 功耗 50W。 电压:+12V 5A ,

+3.3V 6A。 纹波:≤10%