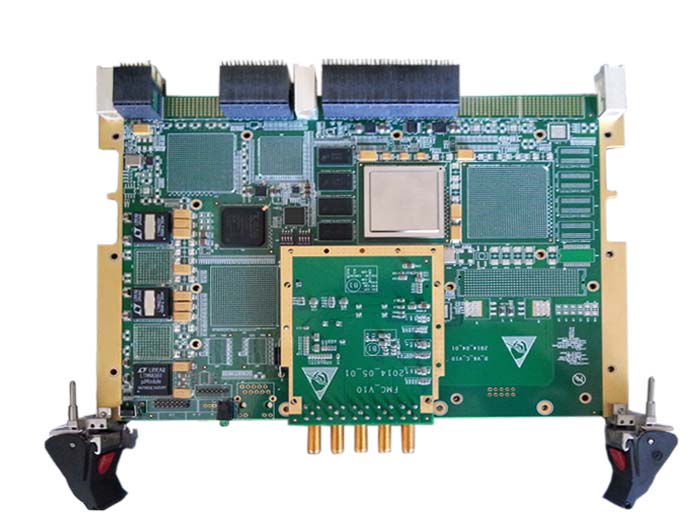

高性能VPX信号处理FMC载板基于6U VPX标准架构。提供2个标准FMC插槽,适用于电子对抗或雷达信号采集、回放及相关处理。FMC载板上主要包含大规模FPGA、大容量DDR3存储器、FMC插槽、扩展IO等。通过使用统一的高性能FMC载板扣接不同的数据接口FMC子卡的方式,可以实现不同采样频率、不同量化位数、不同通道数、不同信号形式的采集、回放功能模块。高性能信号处理FMC载板的原理框图如下图所示:

高性能VPX信号处理FMC载板主要技术指标如下:

1.提供配置FPGA,用于整个系统板卡的复位控制、加载控制。外挂1组 Flash作为板卡ROM存储器。

2.设计为板载2组Xilinx V6 FPGA(可选择只焊接1组),可选配为Virtex-6LX130T、LX240T、LX365T、SX315T、SX475T(本系统选择为LX240T)。 其资源统计如下表所示:

| Device (FFG1156) | Logic | Slices | DSP48E | BRAM | MMCMs | PCI-e Interface | Ethernet | GTXs | Banks | Configruation |

XC6VLX130T | 128000 | 20000 | 480 | 528 | 10 | 2 | 4 | 20 | 15Banks | 43719776 |

XC6VLX195T | 199680 | 31200 | 640 | 688 | 10 | 61552736 | ||||

XC6VLX240T | 241152 | 37680 | 768 | 832 | 12 | 73859552 | ||||

XC6VLX365T | 364032 | 56880 | 576 | 832 | 12 | 96067808 | ||||

XC6VSX315T | 314880 | 49200 | 1344 | 1408 | 12 | 104465888 | ||||

XC6VSX475T | 476160 | 74400 | 2016 | 2128 | 18 | 156689504 |

3.每组FPGA外接2组32bit位宽DDR3 SDRAM。每组512MB,读写时钟1066MHz,读写有效带宽可达3GB。

4.每组FPGA外接1个FMC子卡插座,HPC连接方式,符合Vita57标准。

5.每组FPGA引出12x GTX到VPX背板。8x用于SATA,4x用于PCIe。

6.每组FPGA引出20x LVDS到VPX背板。

7.FPGA加载flash最大容量1Gb,可存储4组XC6VSX475T的加载启动程序,加载程序选择由CPU软件通过配置FPGA控制。

8.提供1组时钟系统用于载板高速GTP参考时钟、FPGA工作时钟。

9.2组FPGA系统默认只用1组,另一组及其外围相关电路不焊接,用于扩展应用。

10.提供备用1组时钟系统用于FMC子卡相关同源时钟系统(默认不使用)。

11.提供调试和面板连接器,将JTAG、灯显信号、测试IO、拨码控制、外部Reset输入等信号引出。

12.VPX背板提供2路RS232串口控制信号。

13.预留IIC总线连接负责系统管理载板和子卡。